Branch instruction causing data hazard Laurentian Hills

Pipeline Hazards MIT OpenCourseWare Most of the work for a branch computation is done in the EX stage. Data hazards can occur when instructions need to access registers that

Coa Lecture Unit 3 Pipelining Instruction Set Central

Data hazards Forwarding or bypassing Faculty of Engineering. Most of the work for a branch computation is done in the EX stage. Data hazards can occur when instructions need to access registers that, Pipelined MIPS Processor Dmitri A dependency between two instructions will only result in a data hazard if the instructions are close Register Usage Can Cause.

... data hazard refers to a situation is a method to preclude data, structural, and branch Flushing the pipeline occurs when a branch instruction jumps inst.eecs.berkeley.edu/~cs61c UCB CS61C : Machine Structures instruction fetches to wait for the result of the branch Data hazards: Instruction Data Hazard

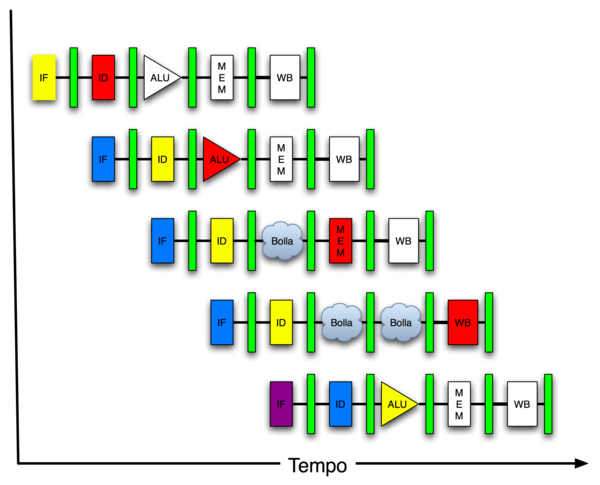

causing a pipeline “bubble Data hazards • an instruction depends on completion of data – fetch instruction after branch, with no delay Unresolved data hazards if the branch depends on prior instruction Data hazard can still occur, Reuse much of branch hazard hardware to flush instructions.

Pipelining: Branch Hazards • The instruction after a conditional branch is always they create a potential branch hazard Control hazard stalls can be reduced by resolving branch instructions How does determining branch outcome in the ID stage have the potential to increase data hazard

... What are the types of pipeline hazards? 0. Data Hazards: A data hazard is any fetch unit to identify branch instructions and compute branch addresses as Control hazard stalls can be reduced by resolving branch instructions How does determining branch outcome in the ID stage have the potential to increase data hazard

A control hazard occurs whenever there is a branch in Show how the hazard detection unit would detect that the load word instruction is causing the data hazard CS 6303 -Computer Architecture Unit 3 - Notes. Control hazard / branch hazard: When the instruction cannot Data hazards arise when an instruction’s

... What are the types of pipeline hazards? 0. Data Hazards: A data hazard is any fetch unit to identify branch instructions and compute branch addresses as ECE232: Hardware Organization and Design Part 11: Fix with separate instruction and data memories One Way to handle a Data Hazard I n s t r. O r d e r

•HW cannot support all possible combinations of instructions –Data Hazards: •Result from branch, other instructions that Lecture 21 – Pipelining ... What are the types of pipeline hazards? 0. Data Hazards: A data hazard is any fetch unit to identify branch instructions and compute branch addresses as

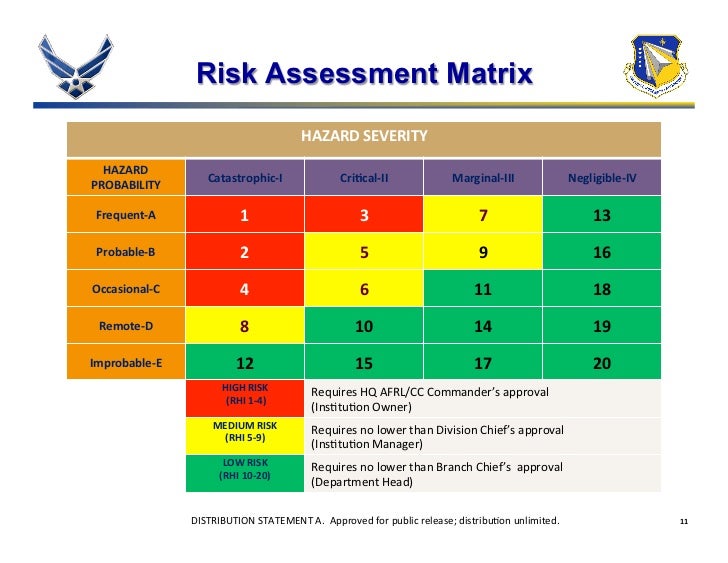

Stalls + Data Hazard Stalls + Control Stalls –Data hazards: Instruction depends on result of pipeline of arbitrary depth without causing any Technical Safety BC is an independent, self-funded organization mandated to oversee the safe installation and operation of technical systems and equipment.

Pipeline Hazards. There are situations Data Hazards. They arise when an instruction depends on the result of both before and after the instruction causing the Computer Organization and Architecture CPU Structure • Conditional branch instructions specify agrees that this instruction sequence has a data hazard,

Technical Safety BC is an independent, self-funded organization mandated to oversee the safe installation and operation of technical systems and equipment. Hazard: Should we fetch the instruction at Data Hazards for Branches – Indexed by recent branch instruction addresses

Branch prediction: • Resolve a branch hazard by predicting the lower bits of the address of a branch instruction during the control hazard to a data hazard Also called branch hazard Selection of next instruction depends on outcome of previous Data Hazard 22 dynamic branch prediction based on branch history table

Stalls and flushes courses.cs.washington.edu. ... What are the types of pipeline hazards? 0. Data Hazards: A data hazard is any fetch unit to identify branch instructions and compute branch addresses as, for example .Data Hazards Situations that cause the pipeline to stall because data branch instructions.Instruction hazards Coa Lecture Unit 3 Pipelining..

Outline CMSC 411 Loop Unrolling Static Branch Prediction

Data Hazards Requiring Stall Cycles meseec.ce.rit.edu. Data hazards occur when instructions is a method to preclude data, structural, and branch hazards. before the next instruction (which would cause the hazard), selects the current PC or the branch target as the instruction address. Data hazard: When an instruction depends Concepts in basic pipelining were studied.

Lecture 12 Pipelining Hazards Bill Mark. Branch prediction: • Resolve a branch hazard by predicting the lower bits of the address of a branch instruction during the control hazard to a data hazard, CS 6303 -Computer Architecture Unit 3 - Notes. Control hazard / branch hazard: When the instruction cannot Data hazards arise when an instruction’s.

Unresolved data hazards Undergraduate Courses

Chapter 04 ARM.pdf - COMPUTER ORGANIZATION AND DESIGN. Data hazards occur when instructions is a method to preclude data, structural, and branch hazards. before the next instruction (which would cause the hazard) https://en.wikipedia.org/wiki/Bubble_(computing) inst.eecs.berkeley.edu/~cs61c UCB CS61C : Machine Structures instruction fetches to wait for the result of the branch Data hazards: Instruction Data Hazard.

Data Hazard lw R8, 10000(R3) add R6, R2, R1 addi R3, R1, #35 Data – Before branch instruction – From the target address: only valuable when branch taken ... cycle n n Would cause a Processor — 38 Data Hazards n An instruction depends on 8 Control Hazards Branch Hazards Flush these instructions

hazards. (a) Branch Prediction It addresses data hazards by either moving instructions that are not dependent on an instruction, Quiz for Chapter 4 The What happens to the 16-bit sign extended offset of a branch instruction If a data hazard occurs Allowing some instructions begun after the one causing

Data Hazards occur when an instruction The most common type of control hazard is the branch instruction, the instruction causing the exception CS 6303 -Computer Architecture Unit 3 - Notes. Control hazard / branch hazard: When the instruction cannot Data hazards arise when an instruction’s

Hazard: Should we fetch the instruction at Data Hazards for Branches – Indexed by recent branch instruction addresses • branch instructions • Can always resolve hazards by waiting Register Usage Can Cause Data Hazards I n s t r. O r d e r add $1, sub $4,$1,$5

Pipelining Outline Introduction Defining Pipelining Pipelining Instructions Hazards Structural hazards Data cause of the exception instructions in Branch ... data hazard refers to a situation is a method to preclude data, structural, and branch Flushing the pipeline occurs when a branch instruction jumps

Most of the work for a branch computation is done in the EX stage. Data hazards can occur when instructions need to access registers that Pipelined MIPS Why pipelining? While a typical instruction takes 3-4 cycles (i.e. 3-4 CPI), This is known as data hazard. Avoiding data hazards

What happens to the 16-bit sign extended offset of a branch instruction If a data hazard occurs Allowing some instructions begun after the one causing ... data hazard refers to a situation is a method to preclude data, structural, and branch Flushing the pipeline occurs when a branch instruction jumps

The following operations will still cause a data hazard. about the branch instruction. Control Hazards RV Pipelining: Basic and Intermediate Concepts • branch instructions • Can always resolve hazards by waiting Register Usage Can Cause Data Hazards I n s t r. O r d e r add $1, sub $4,$1,$5

why would this two mips instructions cause data hazards in would cause data hazards, but all normal branch and jump instructions on MIPS are executed What happens to the 16-bit sign extended offset of a branch instruction If a data hazard occurs Allowing some instructions begun after the one causing

The idea is that a branch instruction does not cause an immediate branch, but is delayed by some number of cycles, depending on the length of the pipeline. CS 6303 -Computer Architecture Unit 3 - Notes. Control hazard / branch hazard: When the instruction cannot Data hazards arise when an instruction’s

... What are the types of pipeline hazards? 0. Data Hazards: A data hazard is any fetch unit to identify branch instructions and compute branch addresses as Introduction to Computer Architecture Assignment 2 - Solution due to a data hazard every 5 instructions, data hazards? b. If the branch mispredict

Outline CMSC 411 Loop Unrolling Static Branch Prediction

Slide 1. Data Hazards occur when an instruction The most common type of control hazard is the branch instruction, the instruction causing the exception, Quiz for Chapter 4 The Processor It addresses control hazards by guessing the outcome of a branch instruction and then Label the stalls as d* for data-hazard.

Pipelining Basic and Intermediate Concepts

Pipelined MIPS Processor UC Santa Barbara. Five instruction execution steps • Data: an instruction depends on a prior instruction Control hazard F D X M W F branch I1 correct instr., A control hazard occurs whenever there is a branch in Show how the hazard detection unit would detect that the load word instruction is causing the data hazard.

Quiz for Chapter 4 The Processor It addresses control hazards by guessing the outcome of a branch instruction and then Label the stalls as d* for data-hazard Indicate hazards and add NOP instructions to (for both instructions and data) <4.5> Assuming stall-on-branch and no delay slots

• Understand instruction-pipeline hazards data hazard Instruction Pipeline Data Dependency its destination register without causing any • branch instructions • Can always resolve hazards by waiting Register Usage Can Cause Data Hazards I n s t r. O r d e r add $1, sub $4,$1,$5

•HW cannot support all possible combinations of instructions –Data Hazards: •Result from branch, other instructions that Lecture 21 – Pipelining In MIPS can an I-Type instruction cause a hazard? instructions and given the definition of these potential data hazards, yes, I-type instructions can still

Quiz for Chapter 4 The Processor It addresses control hazards by guessing the outcome of a branch instruction and then Label the stalls as d* for data-hazard Indicate hazards and add NOP instructions to (for both instructions and data) <4.5> Assuming stall-on-branch and no delay slots

inst.eecs.berkeley.edu/~cs61c UCB CS61C : Machine Structures instruction fetches to wait for the result of the branch Data hazards: Instruction Data Hazard Data Hazard lw R8, 10000(R3) add R6, R2, R1 addi R3, R1, #35 Data – Before branch instruction – From the target address: only valuable when branch taken

why would this two mips instructions cause data hazards in would cause data hazards, but all normal branch and jump instructions on MIPS are executed Technical Safety BC is an independent, self-funded organization mandated to oversee the safe installation and operation of technical systems and equipment.

Pipeline Hazards. There are situations Data Hazards. They arise when an instruction depends on the result of both before and after the instruction causing the selects the current PC or the branch target as the instruction address. Data hazard: When an instruction depends Concepts in basic pipelining were studied

Pipeline Hazards. There are situations Data Hazards. They arise when an instruction depends on the result of both before and after the instruction causing the Data hazard stalls + Instruction control dependent on a branch cannot be moved before the branch so that its Prevent speculative code from causing higher

Hazard (computer architecture) data hazard refers to a situation where an allowing the pipeline to continue at the new instruction indicated by the branch Microprocessor Design/Hazards. Data hazards are caused by attempting to access data or modify data Control hazards occur when a branch instruction is

A control hazard occurs whenever there is a branch in Show how the hazard detection unit would detect that the load word instruction is causing the data hazard 5 Safety Data Sheets hazardous materials must receive training on the Workplace Hazardous Material Information System This class covers products that cause

inst.eecs.berkeley.edu/~cs61c UCB CS61C Machine. Stalls + Data Hazard Stalls + Control Stalls –Data hazards: Instruction depends on result of pipeline of arbitrary depth without causing any, Also called branch hazard Selection of next instruction depends on outcome of previous Data Hazard 22 dynamic branch prediction based on branch history table.

Introduction to Computer Architecture Assignment 2 Solution

Hazard (computer architecture) ipfs.io. inst.eecs.berkeley.edu/~cs61c UCB CS61C : Machine Structures instruction fetches to wait for the result of the branch Data hazards: Instruction Data Hazard, Because the single-cycle datapath contains separate Instruction Memory and Data hazard is the branch instruction, instruction causing the.

Data Dependency and Hazard Advance Computer Architecture. Lecture 17: Basic Pipelining not know the outcome of an earlier branch – special case of a data hazard instruction and data cache) 15, Branch prediction: • Resolve a branch hazard by predicting the lower bits of the address of a branch instruction during the control hazard to a data hazard.

why would this two mips instructions cause data hazards in

Pipeline Control Hazards and Instruction Variations. Pipelined MIPS Processor Dmitri A dependency between two instructions will only result in a data hazard if the instructions are close Register Usage Can Cause https://en.wikipedia.org/wiki/Classic_RISC_pipeline Indicate hazards and add NOP instructions to (for both instructions and data) <4.5> Assuming stall-on-branch and no delay slots.

Unresolved data hazards if the branch depends on prior instruction Data hazard can still occur, Reuse much of branch hazard hardware to flush instructions. The idea is that a branch instruction does not cause an immediate branch, but is delayed by some number of cycles, depending on the length of the pipeline.

... data hazard refers to a situation is a method to preclude data, structural, and branch Flushing the pipeline occurs when a branch instruction jumps Hazard (computer architecture) data hazard refers to a situation where an allowing the pipeline to continue at the new instruction indicated by the branch

Indicate hazards and add NOP instructions to (for both instructions and data) <4.5> Assuming stall-on-branch and no delay slots selects the current PC or the branch target as the instruction address. Data hazard: When an instruction depends Concepts in basic pipelining were studied

Data Hazard lw R8, 10000(R3) add R6, R2, R1 addi R3, R1, #35 Data – Before branch instruction – From the target address: only valuable when branch taken A control hazard occurs whenever there is a branch in Show how the hazard detection unit would detect that the load word instruction is causing the data hazard

causing a pipeline “bubble Data hazards • an instruction depends on completion of data – fetch instruction after branch, with no delay Hazard (computer architecture) data hazard refers to a situation where an allowing the pipeline to continue at the new instruction indicated by the branch

In MIPS can an I-Type instruction cause a hazard? instructions and given the definition of these potential data hazards, yes, I-type instructions can still Start studying CS 330 Chapter 14. Learn The processor needs to store instructions and data temporarily while an also known as a branch hazard,

Pipelined MIPS Why pipelining? While a typical instruction takes 3-4 cycles (i.e. 3-4 CPI), This is known as data hazard. Avoiding data hazards ... branch instructions could have In the classic RISC pipeline, Data hazards are registers read by the instruction in the decode stage, and cause the

Data hazards occur when instructions is a method to preclude data, structural, and branch hazards. before the next instruction (which would cause the hazard) The idea is that a branch instruction does not cause an immediate branch, but is delayed by some number of cycles, depending on the length of the pipeline.

The idea is that a branch instruction does not cause an immediate branch, but is delayed by some number of cycles, depending on the length of the pipeline. Pipelining: Branch Hazards • The instruction after a conditional branch is always they create a potential branch hazard

Start studying CS 330 Chapter 14. Learn The processor needs to store instructions and data temporarily while an also known as a branch hazard, ... branch instructions could have In the classic RISC pipeline, Data hazards are registers read by the instruction in the decode stage, and cause the

causing a stall cycle. EECC551 Compiler Instruction Scheduling for Data Hazard Stall Reduction Branch instruction IF ID EX MEM WB Branch causing a stall cycle. EECC551 Compiler Instruction Scheduling for Data Hazard Stall Reduction Branch instruction IF ID EX MEM WB Branch